PAMĚŤ RAM

Posun významem zkratky RAM - dnes všechny (skoro) jsou s libovolným výběrem, zkratka RAM = RWM, tedy umožňující čtení i zápis.

Statické RAM (SRAM)

- bipolární i unipolární technologie (TTL, ECL, NMOS, CMOS)

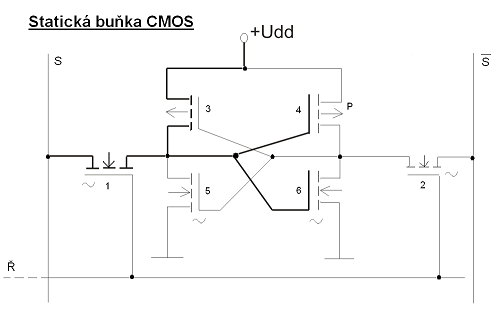

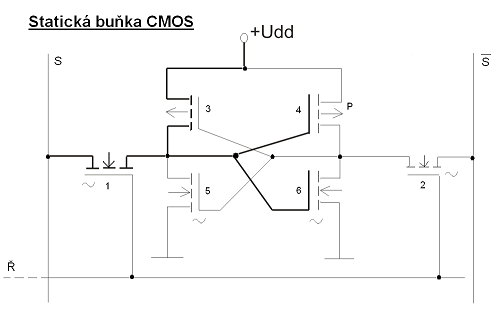

- paměťová buňka: klopný obvod (bist.)+ tranzistory k připojení na sloupcové vodiče

Př.

Ř=1: vybraný řádek, 1 a 2 připojí na S a S stav (výstupy) klopného obvodu 3 až 6

je-li 3 otevřen: na S bude +Udd, tedy 1; zároveň na hradle 6 => S přes 2 uzemněn a hradle 4 - ten je zavřený

Dynamické RAM (DRAM)

- k zapamatování použit paměťový kondenzátor

- tranzistor je spínač - výběr řádky = sepnutí, C se vybije do parazitní kapacity sloupcového vodiče => čtení je destruktivní => nutno obnovovat náboj na C

jednotranzistorová buňka:

- kapacity velmi malé

- nutno užít symetrický čtecí zesilovač => klopný obvod, jeden vstup: čtená buňka, druhý vstup: referenční buňka

- zvyšuje se citlivost zesilovače a omezuje rušení uvnitř

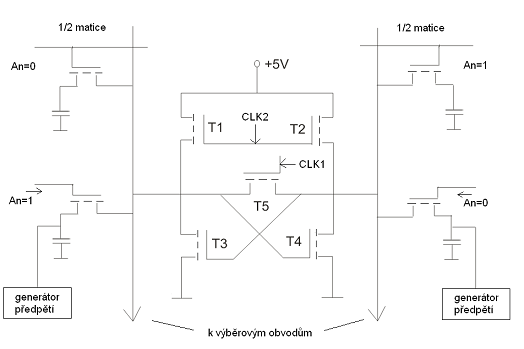

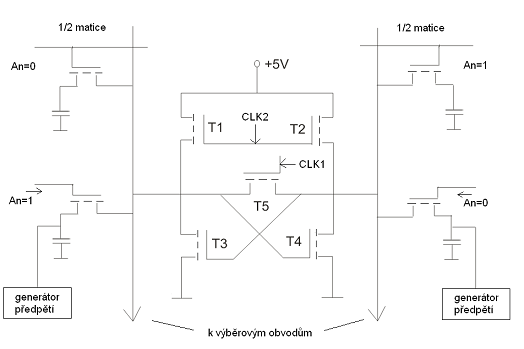

Př.

- zesilovač pro daný sloupec, každý sloupec má svůj

- řízení posunutými fázemi hodin (CLK1 a CLK2)

- v klidovém stavu T1 a T2 zavřeny, nejdřív se zapne T5 a hned po něm T1 a T2, T5 se znovu zavře => bistabil je v rovnovážném stavu, velmi citlivý na nesymetrii na vstupech

- je-li vybrána polovina matice vlevo, porovnává se hodnota U s ref. hodnotou vpravo

- referenční buňka je nabita na 1/2 mezi výstupní napětí paměťové buňky v log.0 a 1.

- klopný obvod (zesilovač) je zároveň tvrdým zdrojem napětí => zpětně nabíjí paměťový kondenzátor

- výstupy z čtecích zesilovačů dále zpracovány výběrovými obvody a výstupními 3 stavovými členy

Refresh:

- obnovení náboje na C (vydrží tam sekundy) - aktivovat řádek

- nutno aktivovat každý (všechny) po určité době

- strategie: blokové (všechny najednou), rozložené (rozloží se na jednotlivé řádky, třeba po 1ms/řádek), transparentní (když se paměť nepotřebuje, což řídí procesor)

Snížení počtu vývodů pouzdra:

Zadávání adresy po částech a jejich ukládání do registru adresy řádků a registru adresy sloupců

- signál RAS (row-address select) - doprovází adresu řádky

- signál CAS (column-address select) - doprovází adresu sloupce

=> zahajují též čtecí či zápisový cyklus, jejich posloupnost slouží jako výběr obvodu (CS)

Dynamické parametry:

- doba cyklu

- vybavovací doba (od RAS, od CAS)

Synchronní DRAM (SDRAM)

- má vstup pro hodinové pulsy - synchronizace signálů uvnitř DRAM

- při dobré organizaci (uložení) dat v paměti stačí zadat adresu sloupce a CAS, pak už není třeba posílat adresu sloupce => dekodér sloupců sám zvyšuje adresu s hodinama (tzn. data, které chceme, musí být na následující adrese - sloupci)

DDR - double data rate (5 ns na data - rychlé)

DRAM:

- jednoduché buňky

- vyšší kapacita než SRAM

- nejlevnější

- vyžadují refresh

- složitější řízení - vyžadují řadič (řídící obvod) - ovládá RAS, CAS, hodiny CLKA, CLKB, R/W,OE